### **Timers and Counters**

#### LISHA/UFSC

#### Prof. Dr. Antônio Augusto Fröhlich Fauze Valério Polpeta Lucas Francisco Wanner

http://www.lisha.ufsc.br/~guto

March 2009

http://www.lisha.ufsc.br/

### **Timers and Counters**

- Devices to keep track of recurring events

- Time

- Elapsed time

- Delays

- Time-outs

- Scheduling

- Types of timers in embedded systems

- Oscillators

- Counters

- Real-time clock

- Watchdog

### Oscillators

- Basic structure

- A charged capacitor connected to an inductor

- The capacitor starts to discharge through the inductor

- At the same time, the inductor creates a magnetic field

- Once the capacitor discharges, the inductor will try to keep the current in the circuit, so it will charge up the other plate of the capacitor

- Once the inductor's field collapses, the capacitor has been recharged (but with the opposite polarity), so it discharges again through the inductor

- A clock generator is a kind of oscillator in which the frequency is controlled by a piezoelectric crystal

- The clock of a timer can be shared with or scaled from the processor's clock

- Clock divisor (e.g. counter)

- Clock multiplier (e.g. pll)

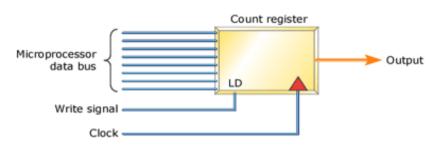

- Basic structure

- Loadable count register

- Input clock signal

- Triggers count operations

- Output signal

- Indicate counting events

- Operation

- Counter is loaded with an initial value

- Each subsequent clock transition increments (decrements) the counter

- When the counter overflows (zeroes), the output signal is asserted

- Can be driven to an interrupt request line or an I/O port for polling

# **Timer Programming**

- Transition trigger

- Level, rising edge, falling edge

- Initial values

- Setable, reloadable

- Precision of count registers (bits)

- Resolution (in hertz)

- Input frequency

- Divisors

- Operations

- Overflow, compare match, input capture

- A real-time clock (RTC) is a battery-powered counter that keeps track of time

- Example: Motorola MC-146818 (PC RTC)

- Keeps track of time and date

- Different registers for second, minute, hour, day, etc.

- ~1Mhz resolution

- BCD or binary format

- Interrupt generation

- Like a timer on clock and counter transitions

- Like an alarm with a predefined time

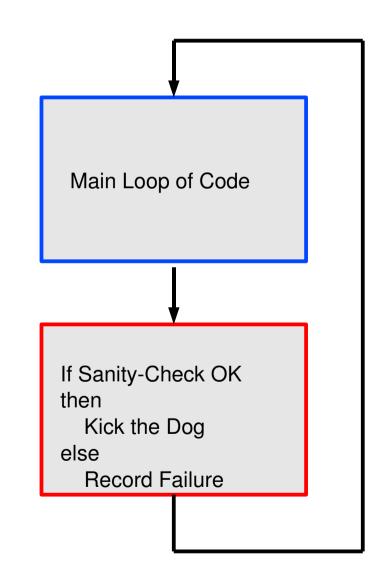

#### Hardware

- A counter with the output signal wired to the circuit's reset

- Initiated with a certain value that is constantly decremented

- Must be reinitialized before reaching zero

- Software

- Sets the count to its original value often enough to ensure that it never reaches zero

- If it does reach zero, it is assumed that the software has failed in some manner and the WDT "bites" the processor, forcing the system to reinitialize itself

## Watchdog Timer Use Cases

- In electrically noisy environments, a power glitch may corrupt the program counter, stack pointer, or data in RAM

- The software would crash almost immediately, even if the code is completely bug free

- Bugs in software can also cause the system to hang, if they lead to an infinite loop, a lost pointer, or a dead-lock condition

- Periodically "kicking the dog" ensures that the software is running properly

# Watchdog Timer: "kicking the dog"

- Kick the dog at the end of every main program loop iteration

- Kick the dog only after the system has passed sanity checks

- Stack depth

- Number of buffers allocated

- Status of some mechanical component

- Status of system flags ...

### Case Study: AVR General Purpose Timers

- 8- and 16-bit timers

- Input frequency prescaled from the system clock

- Watchdog Timer

- Separate, prescalable 1 Mhz oscillator

- Timer events

- Overflow

- Compare match

- Input capture

- Interrupt-based event notification

- Overflow, compare and input capture interrupts

- Controlled by a timer interrupt mask register

# Case Study: AT90S Timers Operation

- Timer input clock configured by registers

- Divided from the system clock

- 8-bit timer (Timer0)

- Only Overflow Interrupt

- 16-bit timer (Timer1)

- Overflow, Compare and Input Capture Interrupts

- Timer value available and settable through registers